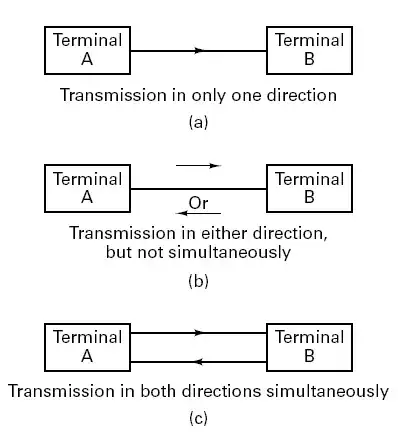

When uC1 wants to talk to uC2 via uart, the Tx of uC1 is connected to Rx of uC2 and vice versa. Half Duplex states that only 1 uC can use the communication line at a time and Full Duplex states that both uC can use the line at the same time. The Tx and Rx pin connections still remain the same for both methods of duplexing, but how 2 different scenarios are possible? Does the presence of separate Buffers for tx and rx determine duplexing or are special IC's and pin connections needed? Im confused because im working on a system where 2 uC's communicate with each other and both can send data at any point of time across a common uart connected to both of them(uC1=UART1,uC2=UART1).This will help me decide if priority among the 2 uC's is needed or not(i.e force them to work in half duplex, cos il be using ACK/NACK for messages sent via uart,and if both can send at any point of time,theres chances of misinterpretation/corruption of data(i.e uC1 is expecting ACK from uC2 in its rx buffer but uC2 is sending a message and not an ACK for the received message)).

Update

Im using 2 LPC1778,where the UART1 TX of uC1 is connected to UART1 RX of uC2 and UART1 RX of uC1 is connected to UART1 TX of uC2. Both uC can send data at any point of time simultaneously(full duplex)and no transceivers will be used(direct uC-uC communication).The uC's have separate Tx and Rx Shift registers. When uC1 is Tx'ng,data is going to uC2 Rx FIFO. If uC2 transmits,data will be going to uC1 Rx FIFO. So, if both uC's send, there wont be any collision right?