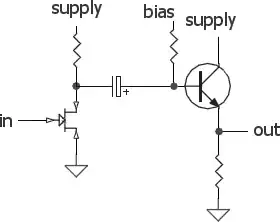

I see this circuit a lot on electret microphone preamps, but I don't quite understand it. The FET is operated as a common source amplifier, so it has gain, inverts, and has relatively high output impedance. So it would make sense to follow it by a buffer.

The BJT is common collector/emitter follower, so it would seem to be acting as just such a buffer, right? It would be non-inverting, with near unity voltage gain, and low output impedance to drive other things without being degraded. The voltage signal from the FET is passed through the capacitor to the base of the BJT, where it's then buffered and shows up at the output of the BJT.

What I don't get is why the FET's drain resistor is connected to the output of the BJT, rather than to the power supply. Is this some kind of feedback? Wouldn't it be positive feedback? (As the FET's output voltage increases, it pushes the base voltage upwards through the cap, which then pushes the output voltage upwards from the BJT, which then pulls the FET voltage upwards, and so on.)

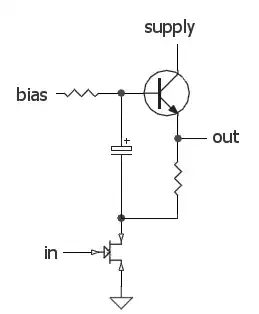

What advantage does it have over a circuit like this?