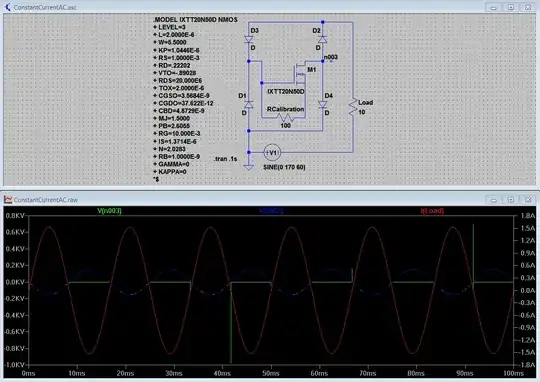

The significance that I usually associate depends on the magnitude of the voltage. I think a good measure of how suspicious/skeptical you should be is how many multiples of the expected value you see (and how many ideal components you use).

- Circuit behavior matches expected results: 3/10

- Output voltage exceeds supply voltage by 50%: 4/10

- Output voltage exceeds supply voltage by 110%: 5/10

- Output voltage exceeds supply voltage by 500%: 8/10

- Output voltage is measured in kV or MV: 10/10

- You have to look up the SI prefix for your voltage or current: 11/10

An extremely relevant quote that applies to modeling is

"Everything should be made as simple as possible, but not simpler."

With ideal circuit elements, it is easy to omit a lot of the parasitic effects in a circuit, such as capacitance, inductance and resistance. Ideal models may not switch operating modes smoothly, and abrupt transitions/discontinuities are also sources of more weird solver behavior. Another thing not handled well is multiple high impedance devices in a voltage divider. Another gotcha is operating a model outside its characterized region.

Beware of simulating circuits you don't understand, as you may not understand the expected behavior or be able to spot when it's misbehaving.