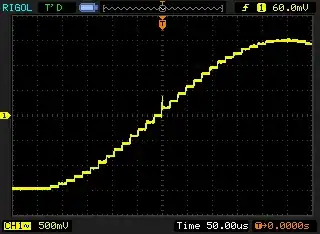

Does anyone recognize this spike in the output of an op amp when the signal crosses 0V? It spikes up when crossing up and down when crossing down. In one of the EEVBlog videos, Dave pointed to something exactly like this on the oscilloscope and said (as an aside) that it could happen when using a 10k feedback resistor or something like that. But I can't remember which video it was. This is the output of a TL071 (actually 1/4 of a TL074). It's fed from the output of 2 other TL071s through 2.2k resistors, and the feedback has a 10k potentiometer.

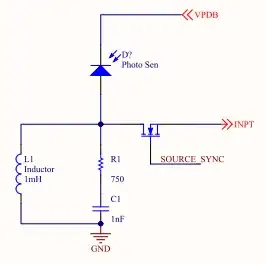

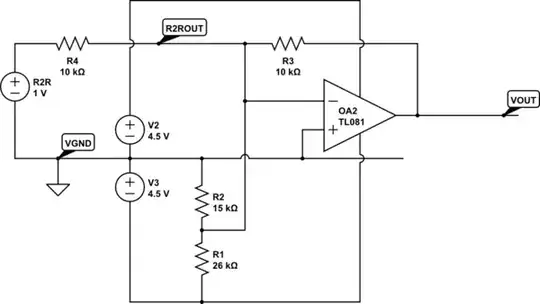

simulate this circuit – Schematic created using CircuitLab

Update March 10

As mentioned in the comments below, the circuit consists of ATmega328P processor driving 8 lines into an R2R DAC. The output of the DAC and a DC bias voltage intended to center the DAC output at 0V feed into an inverting TL071 op amp. The output of this op amp is "OA2OUT" in the schematic above.

The R2R network output has 10k impedance, represented by R4. R1 and R2 give me an offset voltage and have a parallel impedance of 9.5k, which is pretty close to 10k. The feedback resistor R3 is also 10k. So I think that this circuit will sum and invert the R2R and offset voltages.

When I check the output of the R2R network at point R2ROUT, I don't see the spike.

When I check the output of the op amp at VOUT, I see the spike.

I tried a few other things. I tried replacing the 10k feedback resistor with a 2.2k resistor, just because it was lying around and because I remember Dave mentioning something about a 10k resistor in the EEVBlog video. That made the spike worse.

Then I tried replacing the TL074 op amp with an LM6144 op amp. I've been using this circuit to try out various op amps and try to understand what makes them all different, so I know the circuit works (kind of) with all of them. This time I got spikes on every transition.

Finally I tried a TLV2374, which is fantastic, but I still see the spike. It's smaller but still there.

Still trying to figure this one out. Thanks everyone for your help so far!

Update March 13

Tried measuring the R2R output with an R/10 (1k) load as per @WhatRoughBeast comment below. Now I see the spike! Also seems a lot noisier... which is something I noticed before and attempted to fix with 10uF capacitors across the power rails and the virtual ground. It "worked" in the sense that it reduced the noise, but it also introduced the oscillation/ringing that I mentioned when I tried to install a small cap to smooth the DAC output. All these things are obviously related, just not sure how.

By the way I did try the 100 ohm resistor suggested by @Brian Drummond earlier, but the resulting signal was so smeared out and noisy that I couldn't tell what was going on.

So what's the takeaway here? The problem is obviously the MSB behavior that @WhatRoughBeast identified. It, and the noise, seem to get worse with more current through the R2R network. I thought, okay, buffer the R2R signal through a non-inverting op amp before doing anything else with it, but when I do that, I also see the spike. Is the only solution to filter it out and not worry about it?