simulate this circuit – Schematic created using CircuitLab

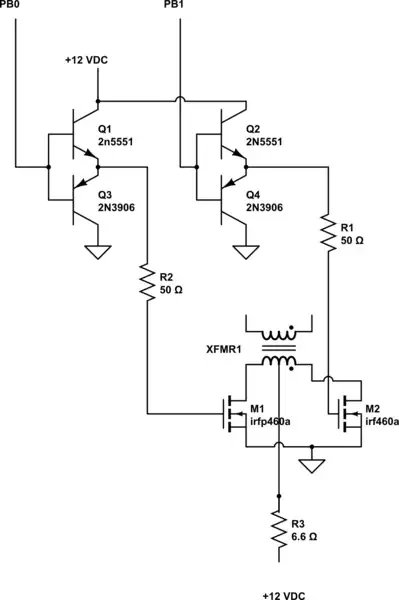

I'm trying to build a "push-pull" switch mode power supply. I'm not entirely sure if that is the right term, but it consists of driving a center-tapped winding on a transformer with just two switching devices. In my case, this design allows me to use two NMOSFETs, which are fairly common parts.

The first thing I did was program an attiny84 to generate a 10 khz square wave. I'm using the 16 bit counter and an interrupt to do this

#define F_CPU 8000000UL

#include <avr/io.h>

#include <util/delay.h>

#include <avr/power.h>

#include <avr/interrupt.h>

#include <stdint.h>

#define HALF_PERIOD 400

int

main (void)

{

clock_prescale_set(clock_div_1);

DDRB |= _BV(DDB0);

DDRB |= _BV(DDB1);

TCCR1B = _BV(CS10);

TCCR1B |= _BV(WGM12);

TIMSK1 = _BV(OCIE1A);

OCR1A = HALF_PERIOD;

PORTB = _BV(PB0);

TCNT1 = 0;

sei();

while(1);

}

ISR(TIM1_COMPA_vect)

{

if(PORTB & _BV(PB0) != 0) {

PORTB = 0;

_delay_loop_1(1);

PORTB = _BV(PB1);

} else {

PORTB = 0;

_delay_loop_1(1);

PORTB = _BV(PB0);

}

}

The logic behind setting OCR1A to 400 is that it should be half the period of the frequency I want to generate. This should generate a 10 kilohertz signal. The interrupt vector calls _delay_loop_1(1) to inject a small amount of dead time. My understanding is that this code should switch between PB0 being high and PB1 being high. I do not have a scope to verify this unfortunately.

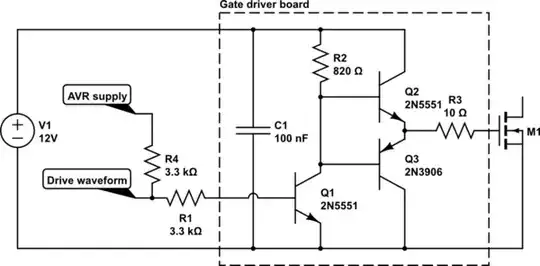

From the outputs PB0 and PB1 I need to drive MOSFETs. My understanding is you shouldn't drive a MOSFET gate directly from the chips digital output pins. The easiest driver circuit I could find was an "emitter-follower" pair.

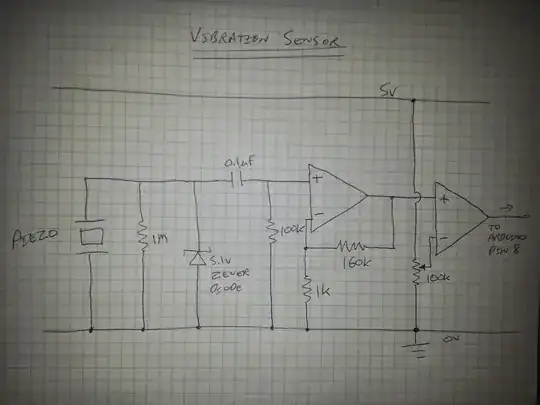

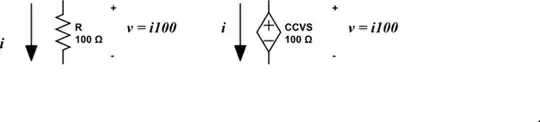

This is the circuit I came up with. I'm driving the gates of the MOSFETs to +12 VDC as well as the center tap of the transformer. The power supply I'm driving it with is rated for 50 amps.

XFMR1 is a transformer I wound myself from a toroid. The cross section is 1.2 square centimeters. It's a 10 turn transformer with a center tap. My logic around the number of turns is +12 VDC is the peak voltage, so the RMS voltage of the circuit is \$12\sqrt2\$. The turns were calculated as follows from here.

\$ N = (E * 10^8) / (4 * f * B * a)\\ E = 8.46\\ f = 10000\\ B = 5000\\ a = 1.2\\ N = \frac{(8.46 * 10^8)}{(4 * 10000 * 5000 * a)}\\ N = 3.53 turns \$

So I used 5 turns to have some safety margin and the total number is doubled since I'm using a center tap. This wastes copper but is simpler. I put a clip lead wound around the corner with a few turns so I can measure output frequency and voltage.

The resistor R3 is there to prevent things from blowing up. In reality it should not be there. If I power up the circuit without the voltage feeding the center tap of the transformer, I can use my Extech MN47 to measure a 9.85 khz signal on the gate and source of each MOSFET. If I put the multimeter in current mode and put it in series with resistor I see 1.4 amps of current flowing continuously. This seems to indicate that something is wrong with my circuit. With the center tap connected, the multimeter indicates a frequency of 24 hz on both the gates and the output coil. I'm assuming something is really wrong with my circuit.

Did I make an elementary error in designing the circuit? Are R1 and R2 chosen correctly?

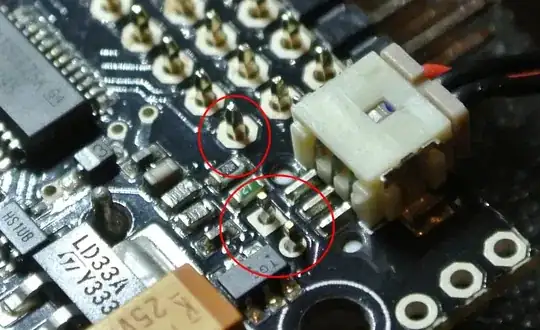

Here is a picture of the circuit, if that makes any difference.

Update 1

I modified my design to the circuit specified by 'jms'. I am using all 2N3906 and 2N3904 now. I found some other MOSFETs in my junk that I am using now. They are MTP50N05Es. These have an Rds of only 0.028 ohms. The drain current is up to 50 amperes. The Vgs is similar at no more than +/- 20 volts. I'm now using 10 ohm resistors to dive the gates from the emitter-follower circuit.

I built the driver circuit onto a perfboard on a small chassis I made. Without the MOSFETs hooked up I can measure a 9.85 khz signal on both the input and output of the circuit. With the MOSFETs connected I can measure only a 13.85 hz signal anywhere in the circuit.

I only have a 50 amp "12 volt" Astron power supply to drive this with. Actual output is closer to 14.5 volts. However, the smoothing capacitors in this power supply are huge. As a result, even with the circuit the voltage from the power supply drops very slowly. If I turn on the driver, connect the center tap and power on the Astron I see 13.85 hz on the output. If I then power off the Astron the voltage drops very slowly. After the voltage drops a bit, the whole thing just works. I can hear an audible ~10 khz tone, measure ~10 khz on the transformer secondary, and measure several volts of AC output on the secondary as well. Of course the capacitors eventually discharge and the circuit turns off. Why does this happen?

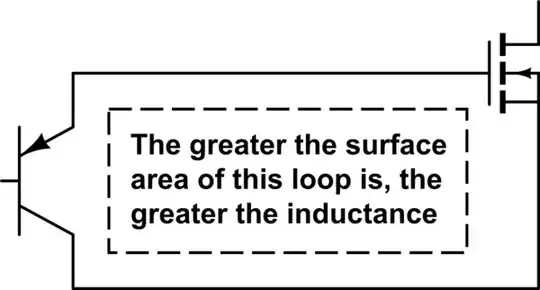

While I attempted to minimize the gate lead length I still wound up with about 3 cm of wire leading up from the perfboard to the gates. Is this enough to cause "ringing" of the gates? Please see the picture, the gate drives are green.

Update 2:

I've also tried moving the MOSFETs down onto the perf board (no heatsink). The gate drive connection is no just a 10 ohms resistor, nothing else. The behavior is identical to what I described above in update 1.

Update 3:

On each emitter-follower pair, I connected a 472K (472,000 pF) round ceramic capacitor directly across the collectors of each transistor.

On the attiny84, I installed a 104K (100,000 pF) ceramic capacitor directly across the VCC and GND of the IC.

The circuit now operates as intended. I am able to measure 9.83 khz output on the secondary of the transformer. I was able to measure 8.81 volts AC as well on the secondary.

With my current limiting resistor installed I saw a current of 0.91 amps in the center tap. With it removed I saw a current of 4.3 amps. This is with no load on the secondary. My conclusion is this core is probably junk, but that is fine.