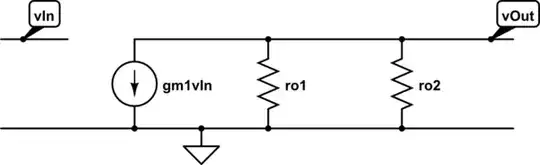

Consider the following circuit, which multiplexes the d0 and d1 inputs to the y output in one clock cycle (i.e., double data rate, DDR).

simulate this circuit – Schematic created using CircuitLab

Which may be the result of synthesizing the following Verilog code:

module ddr_mux (

input wire clk,

input wire d0, d1,

output wire y

);

reg q0, q1;

always @(posedge clk) q0 <= d0;

always @(negedge clk) q1 <= d1;

assign y = clk ? q1 : q0;

endmodule

I have the following timing requirements:

q0must not change while theMUXselect input is at0q1must not change while theMUXselect input is at1

In other words,

ymust have at most two transitions per clock period.

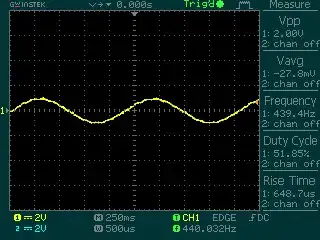

If the synthesis and timing analysis tools do not know these requirements on the y output, they have the freedom to implement the circuit with an arbitrary timing relationship between q0, q1, and sel. Here is an example of how this could go wrong:

And here is the desired behaviour:

How do I correctly express this in the form of SDC constraints to be read by Cadence synthesis and timing analysis tools?