A flip flop is built from two back to back latches with opposite polarity clocks, which form a master slave topology.

The type of latch is irrelevant (JK, SR, D, T) to this constraint, but it is important that the transparency is controlled by some pin (call it clock or enable or whatever you like).

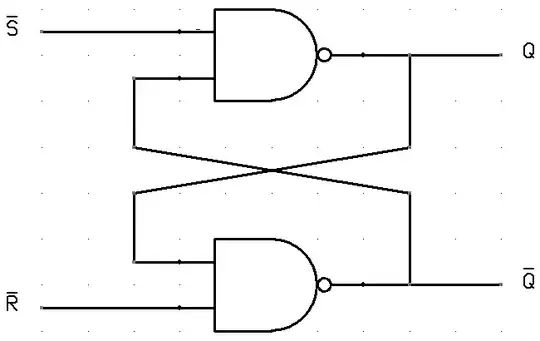

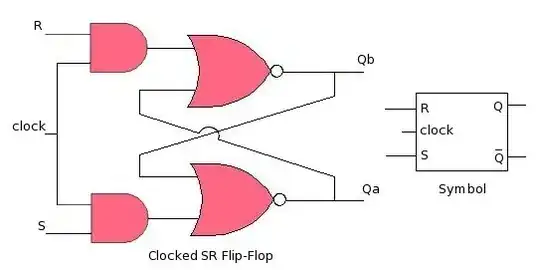

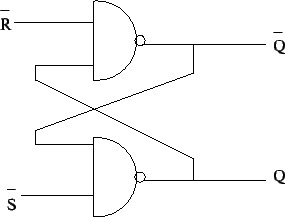

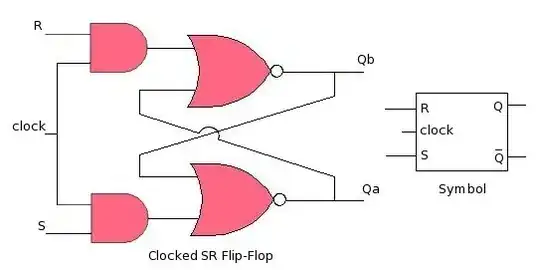

SR latches throw everyone for a loop because the most basic design is transparent all the time. So, once the clock enable is added people start calling it a flip flop. Well, it isn't; it is a gated latch. You can build a SR flip flop out of two gated SR latches however:

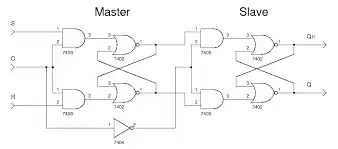

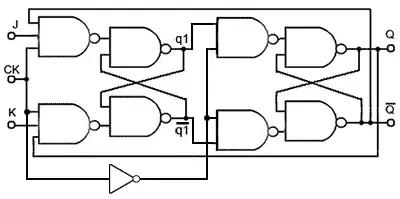

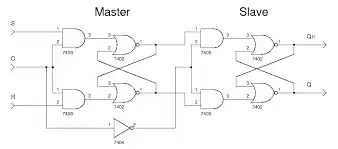

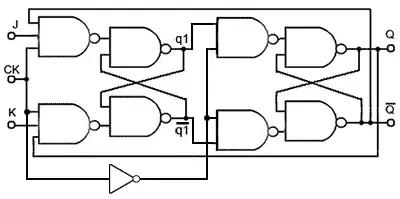

Or two JK latches:

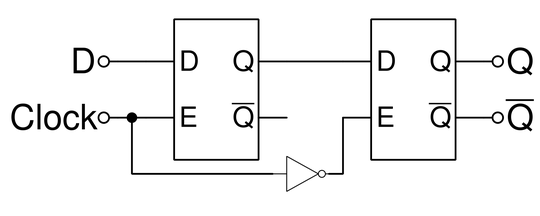

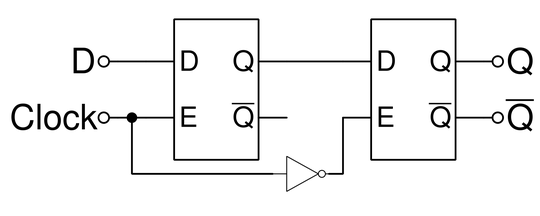

Or two D latches:

Adding a clock pin to a latch (SR or JK) does not make it a flip flop -- it makes it a gated latch. Pulsing the clock to a gated latch does not make it a flip flop either; it makes it a pulse latch (pulse latch description).

Flip flops are edge triggered and the setup and hold times are both relative to this active edge. A traditional flip flop will not allow any time borrowing through cycle borders, since the master-slave topology acts like a lock-and-dam system to create a hard edge at the active clock.

Latches on the other hand setup to the transparency of the latch and hold until the latch closes. They also allow time borrowing through the entire transparency phase. This means that if one half cycle path is slow and the other half cycle path is fast; with a latch based design the slow path can borrow time into the fast paths cycle.

A very common design trick when you need to squeeze every picosecond out of a path is to spread the flip flop apart (into two seperate latches) and do logic in between.

Basically the setup and hold times are completely different between a latch and a flip flop; in terms of how the cycle boundaries are handled. The distinction is important if you do any latch based design. A lot of people (even on this site) will mix the two up. But once you start timing through them the difference becomes crystal clear.

Also see:

good text describing latches and flip flops

What is a flip flop?

Edit:

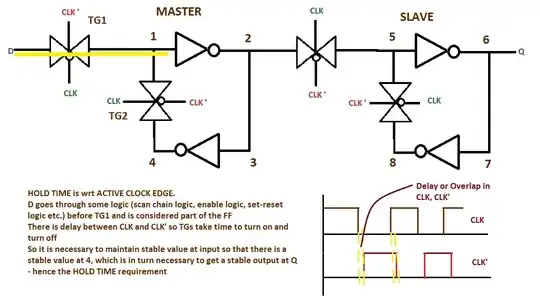

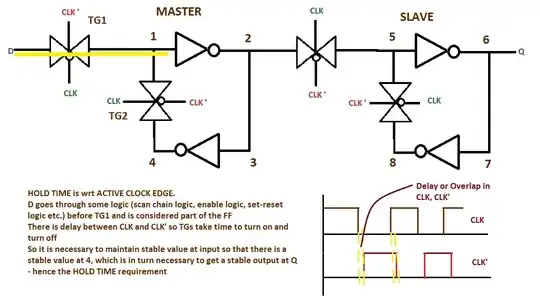

Just showing a t-gate based D-flip flop (notice it is built from two back to back t-gate based D latches with opposite phase clocks).