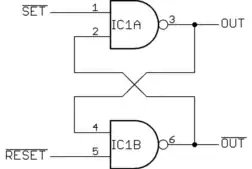

Given an AND gate, an OR gate, and inverters as needed, design an SR flip flop with S and R active low (0).

I understand that to make such a flip flop, I would have to place inverters on the circuit so that the AND and OR gates behave like NOR gates, as NAND with S=0, R=0 would lead to a race condition. However, I have no idea how I would place inverters in such a way for it to behave like NOR gates.