I want to design a four layer PCB, where on the top and second layer are voltage up to 600V present. While I find many information about trace spacing, I don't find anything about isolation between the different layers. Is it possible and safe to have a voltage (difference) of 600V between two (or more) layers? I'm planing to use a normal FR4 PCB and I know the breakdown voltage of 300V/mil. But is the breakdown voltage also safe?

-

1Would be a good idea to contact your PCB vendor, to confirm they can meet your requirements. – MarkU Jan 13 '16 at 01:55

-

1related: [To what extent to I need to be concerned about PCB punch-through when dealing with AC mains?](http://electronics.stackexchange.com/q/77112/7036) – Nick Alexeev Jan 13 '16 at 03:32

2 Answers

Dielectric breakdown for PCB laminates is usually tested to IPC TM-650 test method 2.5.6 for breakdowns across the material and test method 2.5.6.2 for breakdown through the material; i.e. layer to layer.

The text in 2.5.6 is:

This method describes a procedure for determining the ability of rigid insulating materials to resist breakdown parallel to laminations (or in the plane of the material) when subjected to extremely high voltages at standard AC power frequencies of 50-60Hz.

To pass 2.5.6, the dielectric breakdown is >50kV/inch, which gives guidance for Creepage and Clearance rules, as you have already found.

The text for 2.5.6.2 is:

This method describes a technique for evaluating the ability of an insulating material to resist electrical breakdown perpendicular to the plane of the material when subjected to short term, high voltages at standard AC power frequencies of 50-60 Hz.

A pass for test 2.5.6.2 is 30kV/mm or 750V/thou (specification limit). For the thinnest standard laminate thickness of 100 micron / 4 thou, that gives a breakdown voltage of 3kV. Even with moisture absorption, I would not expect 600V to be a problem layer to layer. Note, however, the words "short term". If your setup is going to have much longer than the test with elevated voltages, I would de-rate the breakdown by 50% for some margin.

Layer to layer for any reasonable construction should therefore easily withstand 600V, although as noted, localised voiding can cause lower effective breakdown strengths.

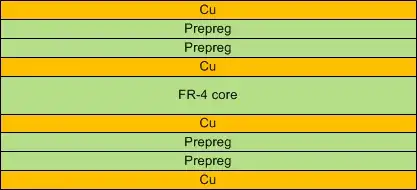

Using a double prepreg (also as noted) is a pretty common thing to do in these cases to avoid voiding issues, so your stack could look something like this:

IPC2221A is the standard, but it tends to be quite conservative (which is a good thing really in HV) but it is also a bit expensive. I do use it extensively, but that is because I design avionics (among other things), where altitude effects are quite critical.

The other comments, such as eliminating sharp corners on tracks, are also a good practise.

- 21,923

- 1

- 29

- 64

Yes you should be fine as long as you take care with the design

The IPC-2221 provides typical electrical properties for common materials (FR4, Polyimide etc... ) & as you stated, the electrical strength is around 39kV/mm.

A copper clad laminate would therefore, in theory, be perfectly capable of withstanding 600V.

That said ... There are a few consideration and not just in the x-y plane with regards to trace separation (again IPC-2221)

Pad & track corner design. Round them off to mitigate buildup of charge & maximise the corona inception voltage. This is a must for medium voltages & not so much with the low voltages of 600V, unless altitude is a real consideration.

FR4 absorbs moisture quite readily & this reduces the electric strength capability.

Prepreg voiding (and also laminations) While in theory the electric strength is 39kV/mm, in practice manufacturing can result in localised areas that do not meet this.

My personal recommendation would be to separate the high voltage via the prepreg instead of the laminate. Double-prepreg the stackup as well to mitigate instance of voiding (what is the probability that two voidings occurrences align? ).