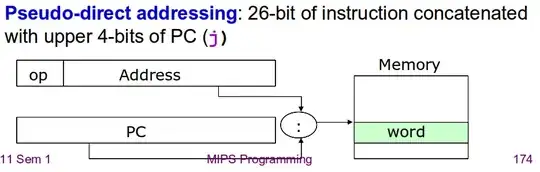

MIPS pseudo-direct addressing takes the upper four bits of the program counter, concatenated with the 26 bits of the direct address from the instruction, concatenated with two bits of 0 0:

PC31...PC28 IM25...IM00 0 0

which creates a complete 32-bit address. This format is used by the J-type instructions, j and jal. Since the upper 4 bits of the PC are used, this constrains the jump target to anywhere within the current 256 MB block of code (1/16 of the total 4 GB address space). To jump anywhere within the 4 GB space, the R-type instructions jr and jalr are used, where the complete 32-bit target address is specified in a register.

The reason for forcing the bottom two bits to 0 is that all instruction addresses in MIPS are 32-bit word aligned, so you can never have a target address of a jump instruction with the two bits anything other than 0 0.