I have a PWM bridge driving a higher than 1k load from 200V supply. The simplified, equivalent schematic is this:

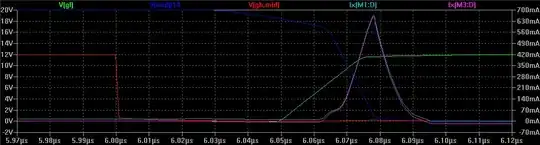

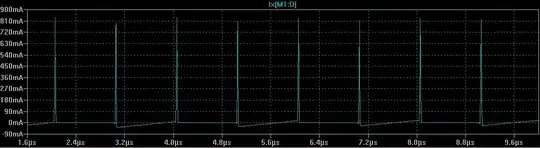

The drivers I'm using are slow turn-on/fast turn-off and, in the schematic, it's a 50% duty-rati.,The parasitics modeled here also involve some capacitance across the filtering inductor. These will cause some spikes, sure, but they pale compared to the switching problem and, while I can get away with 100-200mA peak, what I have here is a bit scary:

The driving, as seen here, is a much nicer version to what will be in reality. The problem is that the mid-point voltage, V(mid), doesn't fall with the ending of the commanding pulse, only with the rising of the complementary pulse, which makes it overlap a bit and cause a spike, in addition to the inevitable parasitic. Here's a zoomed-in portion:

You can see that the upper drive, V(gh,mid), is turned off fast and has plenty of dead-time, while V(mid) keeps on going until V(gl) starts.

I know there are circuits trying to circumvent the parasitic capacity, but they only affect the response (slow zero as opposed to a notch), because the current as seen from the bridge is still there, which is what is the problem.

My question(s): is there any way of making V(mid) fall with the end of the command pulse, actually having a dead-time in there? Another winding with a forced current, maybe? Some clever snubbers? Anything? Or is this "unobtainium"?

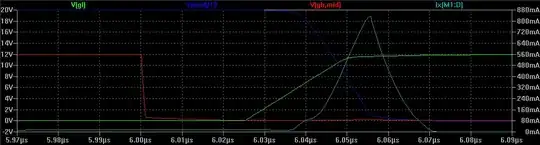

Update: This is a close-up with Id(M3):

The dead-time is 25n but the rise time is imposed to be 25n, too. Tfall=1n but, apparently it doesn't affect the response as I'd want. Increasing the dead-time to 50n (keeping tr) results in this: