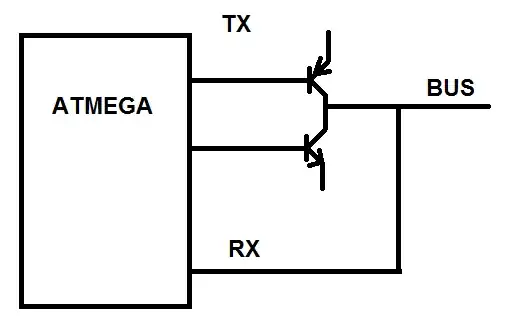

I use the normal ATmega UART interface, but disable the TX part (make it high impedance). To have more push-pull power for a long bus, I use two I/O pins for TX; the PNP and NPN transistors will be actived in the order that prevent a short (I usually use this PNP/NPN pair to drive a MOSFET at high speed, and it worked OK). Only one device can drive the bus at a time, others deactive both BJT transistors to make it high impedance.

I have to bitbang the TX part, but I think it's not very difficult (correct me if I'm wrong). The bit rate doesn't need to be high, but the lowest possible the UART interfaces can receive.

Does this sound feasible? I need your thought.

The NPN transistor's emitter connects to GND, and the PNP transistor's emitter connects to 5 V. There is a 220 ohm resistor at the bases.