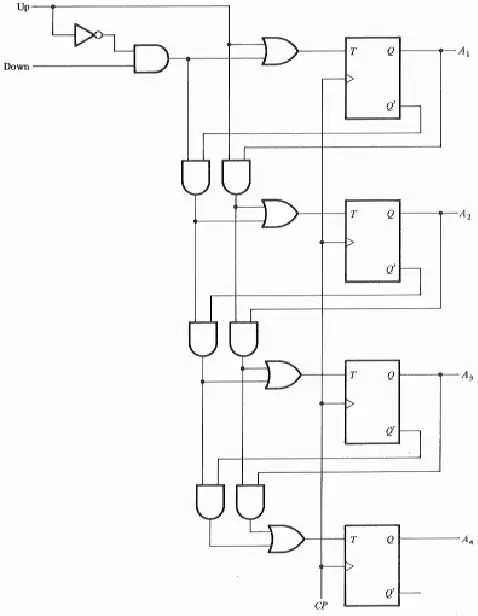

I am trying to understand how to implement up/down binary ripple counter. Basically, I have a bunch of D-flipflops, and connect clk of next flipflop to ether Q or Q'.

So, if I want to change direction of counting, I just switch all clk multiplexors between Q and Q', and counter starts counting in opposite direction.

The problem though is that when I do switch inputs between Q and Q' flipflops do 1 count, so my counter is counting from different number.

I.e. I cannot have something like: 0->1->2->3(direction change)->2->1->0, it's getting like 0->1->2->3(direction change)->c->b->a->9...

What am I missing?