Some background, though I'm not sure if it'll be relevant to my question:

In my design, I have two power stages, a 1st stage PFC boost converter, and a second stage asymmetric halfbridge (I'm using the NCP1605 and FSFA2100 control ICs, respectively, if that's helpful). My goal is to hold off power from the 2nd stage chip until the first stage is up and running. To that end, I've come up with the below circuit, however it isn't working as I'd expect.

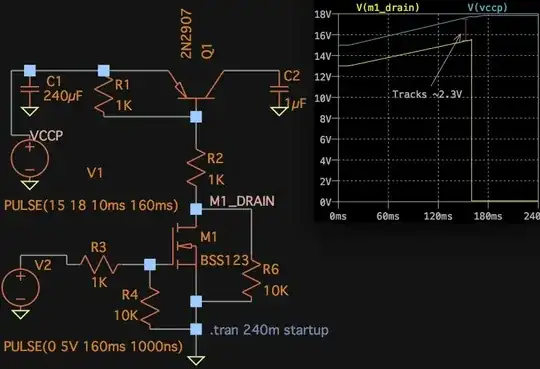

My intention was that VCCP would charge up to about 18V during startup, which happens just fine. VCCP powers the first stage chip. Once it has started up and is regulating properly, pfcOK goes high (to 5V). pfcOK is grounded, otherwise. When pfcOK goes high, it turns on M1, a logic level FET. Turning that on pulls current out of the base of Q1, connecting VCCP with VCCP_FSFA, which is the power to the 2nd stage chip.

I've attached a scope shot showing what actually happens. Blue is VCCP, Purple is VCCP_FSFA, and Yellow is the drain of M1. Ignore green - it's unconnected. You'll see the the drain follows VCCP until just before the middle of the plot, when it drops to ground. This is expected - it pulls low when pfcOK goes high and turns on M1. Prior to that happening, though, VCCP_FSFA oscillates a few times. It appears as if Q1 is turning partially on and off a few times before saturating when M1 turns on. I'm a little confused as to how that's happening. Any thoughts would be appreciated.

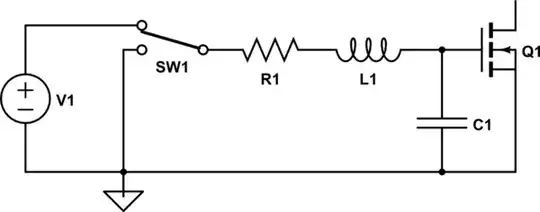

simulate this circuit – Schematic created using CircuitLab