We have some controlled impedance traces on layer 4 of a board. Layer 3 is a GND plane. Layer 5 is a 3.3V plane. Both planes are unbroken (they occupy the entire layer), with the exception of vias and holes.

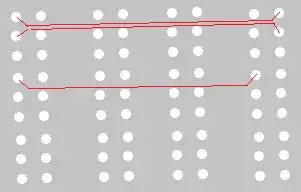

There are a lot of holes on this PCB, because we have a lot of through-hole connectors. See the not-so-pretty picture below:

The white circles are the holes in the PCB. My question is, how do all these holes affect the impedance of the traces? Is there a minimum distance that should be maintained from the holes to ensure that the impedance is within specified tolerances (100ohms +- %5-10 for differential lines for example)

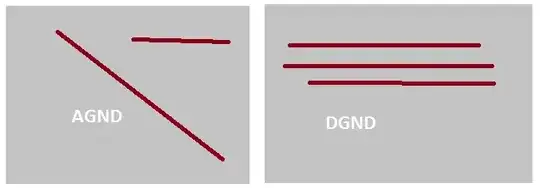

Another somewhat similar question: Consider the picture below:

Let's assume that layer 3, the GND plane layer is now split into 2, one AGND and one DGND section. Do the traces running entirely on a single plane layer (like in the picture) maintain the controlled impedance value? Is there a limit to how close they can get to the edges of the planes before starting to show deviations from the target characteristic impedance?