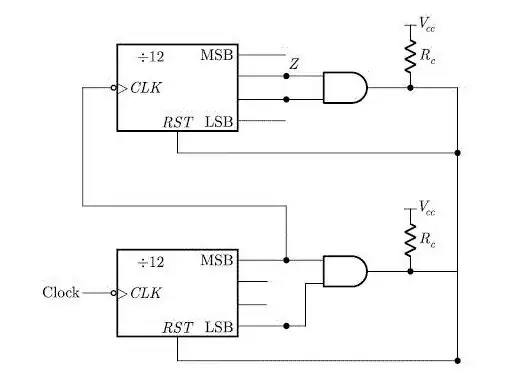

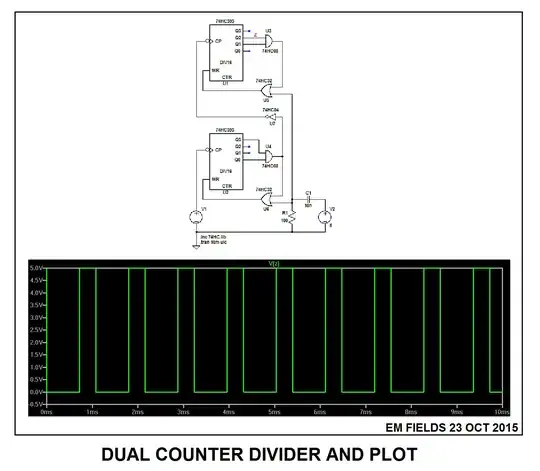

What is the Frequency and Duty cycle and of the waveform at Z (say if input clock frequency is 1.5Khz)

My Understanding:

Two negative edge triggered MOD 12 counters cascaded and reset when the upper counter is at 0110 and lower counter is at 1001.

I know that the upper counter is fed with a clock of f/12 if the input clock frequency of the lower flop is f Hz.

The lower counter has 9 states while upper counter has 6 states.Usually when we cascade MOD N and MOD M counters total number of states is M x N.

The lower counter is MOD 9 and upper counter is MOD 6 and since i am taking the bit next to MSB of the upper counter as the output The frequency should be :

f/9 *1/6 *2 =f/108 Hz

But, for f= 1.215 KHz, the actual answer is 15 Hz but i get 45 Hz.

My doubts:

- Since the upper counter is driven by a different clock, how can is calculate the TOTAL number of STATES of this cascaded asynchronous counter setup?

2.How can i get the duty cycle at the Z output??