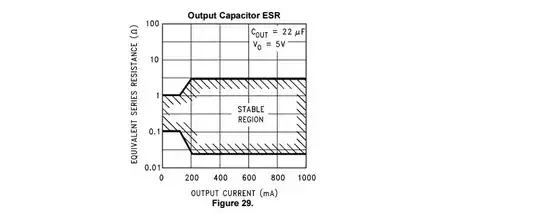

I'm encountering some instabilities in my regulated voltage supply. In short, the system is comprised of a High Power AC device and an MCU sub-system used for automation. The transformer is producing the expected output and this is full-wave rectified & smoothed (etc etc...) as per many of my previous designs. However, I have found that higher-frequency fluctuations in voltage are not properly regulated by the LM2940, causing intermittent brown-out of the MCU.

A scope reading shows that these fluctuations are around ±0.7V either side of the desired 5V, and at a frequency of around 18MHz:

Does anyone have any ideas how I might stabilize this output? Or offer an alternative regulator that is more linear at high frequency (As suggested in this answer)?

For reference, this is the LM2940 datasheet.

Any advice or pointers will be much appreciated!

EDIT: Schematic of the regulation circuit. The 3.3V reg can be ignored as I've tested the 5V output with & without the 3.3V reg... with the same resulting output.

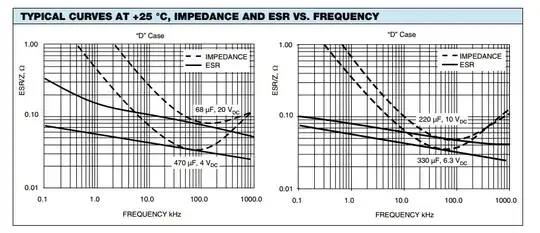

EDIT: Output capacitor C3 is a 100uF Vishay SMD Tantalum, part num TR3C107K010C0100, with max ESR of 0.1Ω