I was surprised to see how flipflops change output on the rising edge of clock signal

-

In addition to what's written below, you should read about the [master-slave flip-flop](https://en.wikipedia.org/wiki/Flip-flop_(electronics)#Master.E2.80.93slave_edge-triggered_D_flip-flop). It doesn't actually have any specific circuit to detect an edge, it just behaves as if it does. – The Photon Oct 01 '15 at 05:37

-

2What are you asking?? – Scott Seidman Oct 01 '15 at 21:26

1 Answers

Rising and failing edges can be detected in several ways.

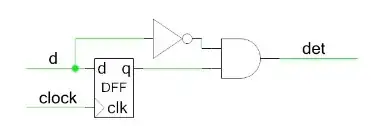

One is to add an additional flip-flop which serves a a simple state machine, so that only transitions from 0 to 1 are used and transitions from 1 to 0 are ignored.

Here is the equivalent for a falling edge detector:

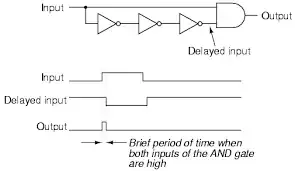

Another is to use a short delay line, such as three 74HCT04 inverters, which results in a pulse being generated for a rising edge, but no pulse for a falling edge. The length of the pulse is the length of the delay line.

And then one could use a monostable, such as a 555 or 74123, to generate a short pulse on the rising edge. (For the 555, an inverter would need to be added in front of the Trigger input, since 555 triggers on the falling edge. For a falling edge detector, no inverter is needed.)

- 47,708

- 5

- 97

- 161