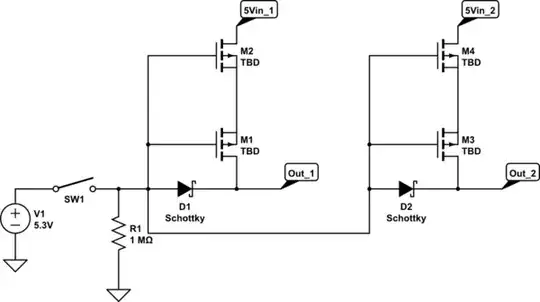

I'm planning to use a chip with two 5V output pins to provide power to two systems: a MCU (attiny85, operating voltage: ~2V - ~5V) and a USB device (input current: 3A). On top of that, I'll have an alternative 5.3V input source to power these systems.

I think the chip's 5V pins will need to be protected from current flow when the alternative source is active. I believe I could perhaps use two sets MOSFETs back-to-back and two Schottky diodes for the required circuitry. The diode will likely have a 300mA - 400mA voltage drop, which is why the alternative source is boosted to 5.3V to accommodate the voltage drops.

I'm very new to designing transistor circuits, so please bear with me. Is the following a good circuit for the task? I'm thinking of using Si2305CDS, which I just happened to find on Digikey and seems to have the right Vgs.

I added a 100r to each gate and a 1M to GND by following this answer. The idea is to block current flow in PIN 1 and PIN 2 when VDD is active. Is this the entire circuitry required? Are there things one should look out for?

Any advice will be much appreciated.

Thanks

EDIT: Fixed MOSFETS. Thanks to @mkeith.