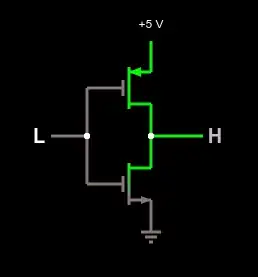

I know that a NOT gate always inverts its input.

When the input is "ON" I can imagine the gate stopping the flow of current.

But how does the gate generates flow of current when the input is OFF?

Please could you explain how this happens as simply as possible, I'm new to electronics ;)