To take some questions you've asked in reverse order:

VHDL is a hardware based language.

It's a hardware description language.

Thus, all of the keyword must have

one representation in real life.

Not everything you can write in VHDL can be mapped onto real hardware (think access types, which are like pointers). Some of these non-synthesisable bits are very useful for modelling your real hardware in simulations without having to get into low-level nitty gritty like you have to for synthesisable code.

What are the representations of the following keywords ?

Often it depends on context:

<=

A signal assignment - it drives a value onto a signal. If that happens from within a clocked process you get a flipflop as the driver (potentially with some gates feeding its D input). If (as in your examples) you are using it in continuous assignments, you just get the logic gates.

:=

A variable assignment - this creates some logic gates. If you read the variable "above" the assignment in the process, you also get a flipflop.

process

with a clock signal in the sensitivity list and an if rising_edge(clk) type construct, this can be used to infer flipflops. In synthesisable code I avoid using processes for anything other than clocked logic. In non-synthesisable code, you can use waits and other control flow structures to do behavioural modelling of external hardware.

entity

See this question: VHDL: Component vs Entity

wait

In terms of real hardware, a process with wait until rising_edge(clk) can be used to infer flipflops: http://www.parallelpoints.com/node/69 . In simulation you can wait for a wider variety of things, including simulated time.

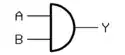

if-then

case

Some "selection" logic (like a mux for example)

while

for

Loops in clocked processes, can be used for various things for example as shorthand to do the same thing to lots of array elements all at once in a single clock cycle.

I have no idea about your last question, the loop you show has an index which is not used within the loop, so it will just be ignored (you're just doing exactly the same thing over and over again)