I'm making my design with Vivado HLs and Vivado and I'm doing some somewhat big transfers between DDR and my custom IP block and vice-versa.

Each transfer from DDR to custom IP is of 256x256x4=262144 bytes and it happens 4 times.

My MM2S (Memory Mapped to Stream) velocity is at 350Mbytes/s and by S2MM is at 200 Mbytes/s.

I know I can get better velocities and I guess these slow ones are related to the parameters of the Axi DMA block.

That's what I came here to ask you, to help me understand which should be the correct parameters since I still can't understand it from reading the logicore product guide.

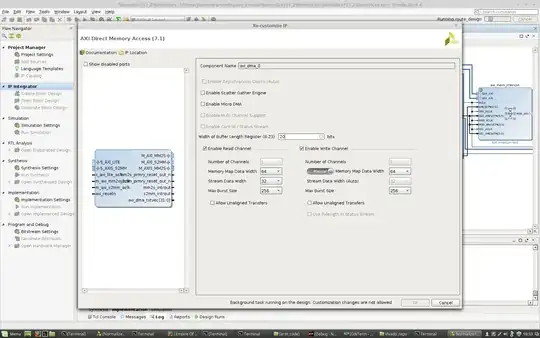

Width of buffer length n From what I understand this is the maximum length of the transfer in bytes like so 2^n. So in my case as 2^18=262144 shall I put 18 in here?

Memory Map Data Width

Data width in bits of the AXI MM2S Memory Map Read data bus. I have no idea here. My words have 32 bits and I defined the entrance stream of my block to have a length of 32 bits but what is this?

Stream Data Width I guess here I should put 32 correct?

Max Burst Size

Burst partition granularity setting. This setting specifies the maximum size of the burst cycles on the AXI4-Memory Map side of MM2S. Valid values are 2, 4, 8,16, 32, 64, 128, and 256.

Again, I have no idea what to put here.

I could do a trial-and-error approach and change parameters until I find the best ones but the problem is that each re-synthesyze and re-implementation in Vivado takes a lot of time...