I am toying with designing a simple 8-bit CPU out of basic logic components. I have a fairly good idea of how my ALU and registers will interact, but the one thing I feel can use some improvement is how to toggle when a line is allowed to connect to the main data bus.

My initial thought was to use and gates to drive the bus. The output from the various lines in the ALU could all go into a set of quad-AND chips that output onto the bus. Only one set of AND gates at a time would have all of its B inputs pulled high to let it out onto the bus.

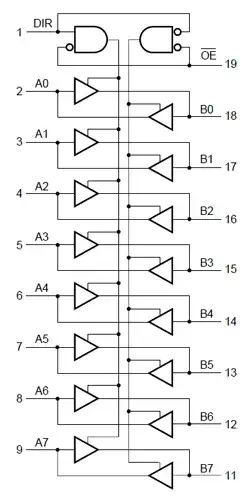

A couple of things I am unsure about: It seems wasteful to use eight full AND gates per line, when I only need one control line going in. Is there a better chip more suited to this purpose? I'm sure I could also do it with eight transistors, but I would like to stick with fairly common (and cheap) ICs.

A solution like this only lets data flow one way from the bus. Is this a problem? I think not, since I have other control lines stopping registers from loading the bus data until I want them to.

Is there a standard chip to use for a bus gate like this?