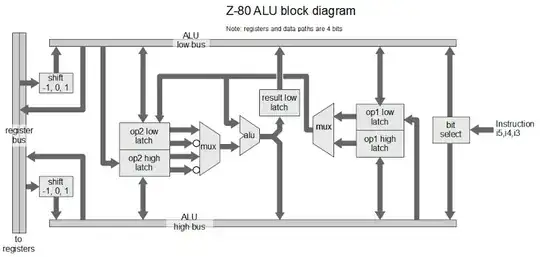

Z80 was a popular 8-bit processor with a 4-bit ALU.

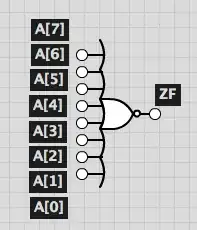

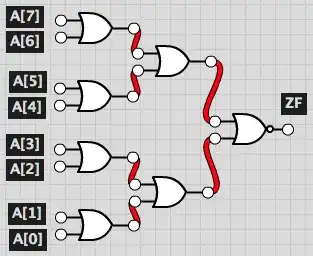

Implementing a zero flag for a register should be straight forward, it would be a logical NOR of all the bits on the register.

Something like that would work for a small number of inputs. As for a 64-bit processor you cannot make one gigantic NOR gate with 64 inputs. The fan-in would be too high. Too many transistors would be in series.

So, I can see some other options (non-exhaustive list).

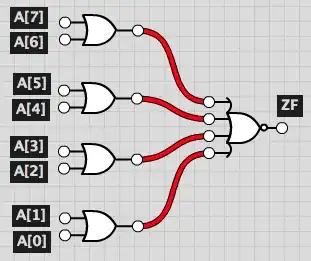

- The zero flag could be generated directly from the 8-bit result using 2 level logic.

- The zero flag could be generated directly from the 8-bit result using 3 level logic.

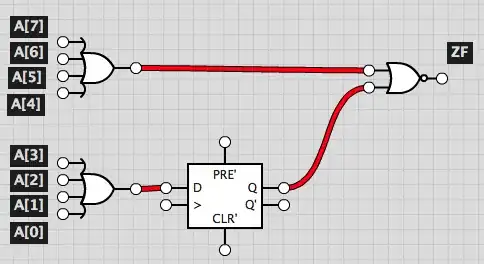

- The zero flag could be generated from each nibble and then put together, like if there was a "half"-zero flag. The result for the lower would be saved using a flip-flop while waiting for the high nibble result to be calculated.

Ken Shirriff wrote a nice article about reverse engineering the Z80 ALU. However when it comes to the zero flag he states:

Not shown in the block diagram are the simple circuits to compute parity, test for zero, and check if a 4-bit value is less than 10. These values are used to set the condition flags.

So, although they are simple circuits I would like to know exactly how they were implemented and if they used any of the implementations proposed above or something else completely different.

There is a related question where they talk about zero flag implementation in general terms.