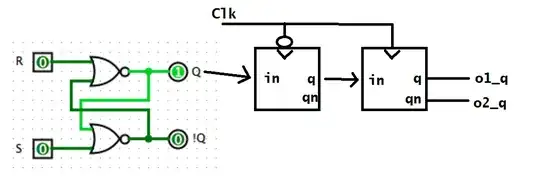

It looks like your latches are not clocked.

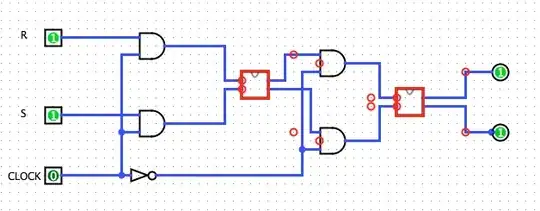

A clock signal needs to go to each of the red squares. For a rising edge master slave flip flop, the master latch (first latch) needs to be transparent when clock is low. The slave latch (second latch) needs to be transparent when the clock is high. So, give the first latch inverted clock, and the second latch clock. Invert this and you will get a falling edge triggered flip flop.

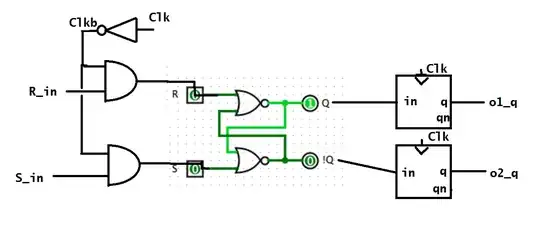

Here are two ways.

Not sure if you want to use the extra AND gates to synchronize the SR portion.

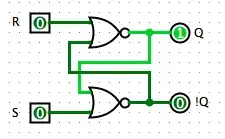

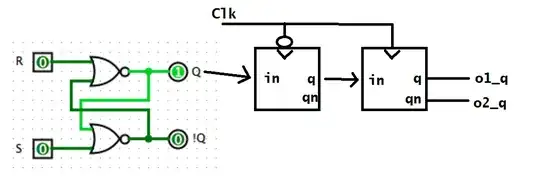

If not you can save the gates:

There might be other ways to do it.

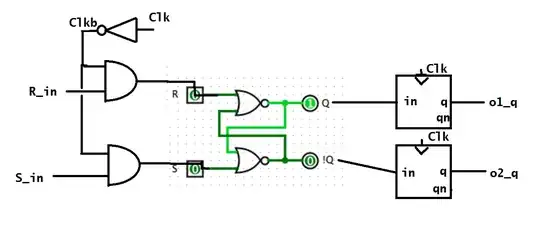

The SR latch is asynchronous to clock, it changes whenever inputs come. The outputs are synchronized with the latches. During the low clock phase, the first latch is open. Q from the RS latch is transparent. Once the clock rises, the first latch closes, and holds its internal state. At the same time, the second latch becomes transparent. It takes the value from the first latch and pipes it to the output. Since the first input was R (the way I have it hooked up), the R signal is produced at o1_q during at the rising edge. Its inversion is S.