How can I find Gate Delay for bit 1 of the sum by a 4-bit look-ahead carry adder?

How can I find Gate Delay for bit 1 of the sum by a 4-bit look-ahead carry adder?

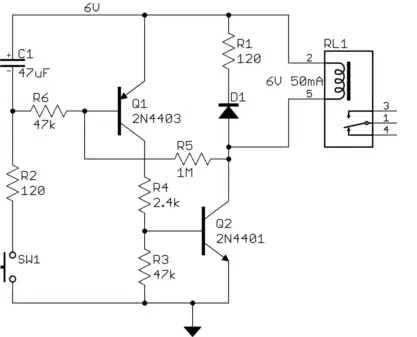

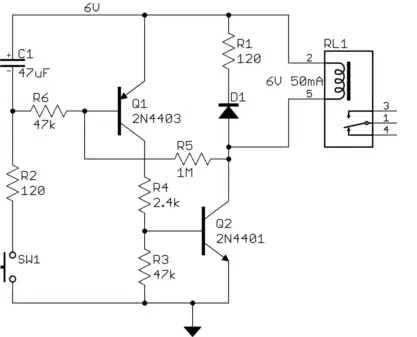

You want to take the internal logic for a 4-bit adder with look-ahead carry, such as the 74HC283:

and then count up the longest possible gate delay for S2, or bit 1 (I get 6).