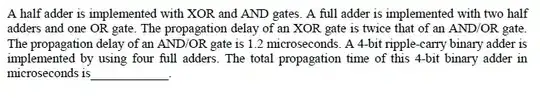

In pic below I have drawn a full adder and mentioned their delays, please help me to verify my answer.

In pic below I have drawn a full adder and mentioned their delays, please help me to verify my answer.

Your analysis of the single full adder is correct as far as it goes, but it is incomplete.

The delays you show are all based on the Xi and Yi inputs. But the delays from the Ci input are different, since they don't go through the first half adder.

The reason this is important is that when you combine the full adders together to create a 4-bit adder, the Ci to Ci+1 delay is a key component of the "critical path" to the upper output bits and the final carry output.

When doing this sort of timing analysis, you need to consider the delays from each input to each output, and use the appropriate delay when combining modules together to form larger structures.

It took me a while but here's how it is :

The first carry and sum will be available after 4.8 us. This should be straight forward.

However, for the subsequent stages, you need to keep in mind that the output of half adders is already there at 2.4 us. So in a sense, it is already computed. The remaining half adder for each full adder is just waiting for the previous carry, which when available from the previous stage can be processed in 2.4 us. So each next stage will take only 2.4 us each.

The catch here is that half of the output in each next stage is already computed, only half needs to be processed.