You could easily do a highly flexible DDS on an STM32F4 Discovery board for ~$15 using an internal DAC, DMA, a timer and a sine lookup table. People have blogged examples of similar things if you look for them.

In order to get the required frequency (the STM32F4xx DAC's can only do 300ksps at full swing, which equates to ~1V/\$\mu\$s) you will need to constrain the range of the DAC.

For a sinusoid, maximum slew rate (in V/s) is \$2 \pi \times f \times A\$.

Inserting the values from the OP's requirements and assuming Vref of the DAC is 3.3V (which if I recall correctly is the case for an STM32F4Disco), a 3.3Vpp sine wave at 100kHz, max slew rate is \$2 \pi \times 10^5 \times 3.3 / 2 = 1036726\$V/s, or \$\approx1.04\$V/\$\mu\$s.

In order to comply with this constraint, the sine wave's amplitude has to be limited, from \$3.3\$V to \$3.3 \times 1 / 1.04 = 3.18\$V.

This now brings in the apparent issue of the 300ksps limit on the STM32F4 DAC. That limit is a furphy. I don't know what the actual physical upper limit is, but I suspect it's the APB1 bus speed. I do know (because I've done it) that you can write at least 2Msps to the DAC and as long as you respect the 1V/us slew rate it will behave predictably. So, you can do 16 samples per cycle for a 100kHz sine wave, a 1.6Msps update rate, as long as you limit the sine wave amplitude to 3.18V instead of 3.3V.

Or, forget the DAC, and use I2S instead. The STM32F411 datasheet says

"Up to 5 SPI/I2Ss (up to 50 Mbit/s, SPI or I2S audio protocol), SPI2 and SPI3 with muxed full-duplex I2S to achieve audio class accuracy via internal audio PLL or external clock."

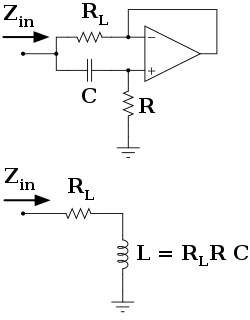

At some point you're probably going to have to deal with digital pots because the reality is that if you want a smooth, continuous output signal, particularly at low speed, then you're going to have to run your DDS through a filter, and that filter is going to have to be adjustable - you can't just put a 100kHz LPF on it and expect it to be useful at sub-1Hz frequencies.