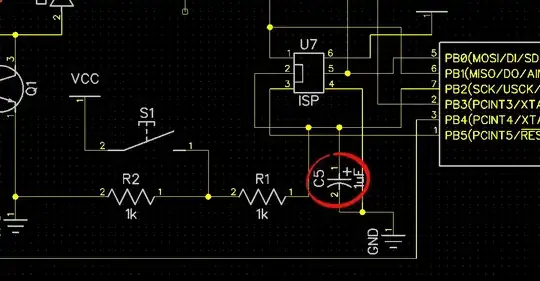

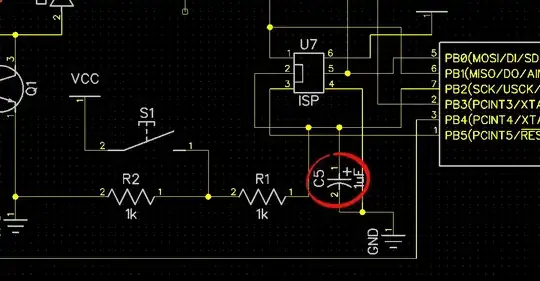

I am trying to make a JK flip flop circuit in proteus but 2 of the nand gates does not seem to be working. There are no errors provided. Two of the 2-input nand gates does not seem to show output when one of the signal is neither red or blue.

I am trying to make a JK flip flop circuit in proteus but 2 of the nand gates does not seem to be working. There are no errors provided. Two of the 2-input nand gates does not seem to show output when one of the signal is neither red or blue.

The grey signals are "unknown", and they propagate through the gates, eventually being fed back to the input, so the unknown state persists. This is something of a quirk with logic simulators, but also something of a warning. It indicates that you may not be able to predict how the circuit powers up. In real life, the state will randomly come up as 1 or 0, and the circuit proceeds from there. But in the absolutely strict environment of the simulator, unknown is unknown.

You can get the circuit to "stabilize" by temporarily forcing those signals high or low (with more parts required). You may also find some help by reading this question

Instead of connecting 'J' and 'K' to the ground or power, try to use the "toggle" component.

Also the circuit diagram should be looking like this : http://upload.wikimedia.org/wikipedia/commons/f/ff/JK-FlipFlop_(4-NAND).PNG

It seems another probability could be that you deleted the info on the NAND gate so proteus does not recognize the component. Try deleting and replacing with another one, this time do not change any names.