I am trying to understand what a D flip flop does int he context of building a truth table, so I can design a synchronous divide-by-five circuit. That is, count to five and reset.

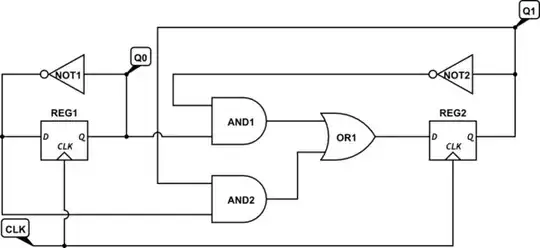

I know I need 3 bits to do this. So Q0, Q1, and Q2 will be my bits.

Now, when I build a truth table, it looks like this:

$$ \begin{array}{lll|lll} \text{Q0} & \text{Q1} & \text{Q2} & \text{D0} & \text{D1} & \text{D2} \\ \hline 0 & 0 & 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & ? & ? & ? \\ 0 & 1 & 1 & ? & ? & ? \\ 1 & 0 & 0 & ? & ? & ? \\ 1 & 0 & 1 & ? & ? & ? \\ 1 & 1 & 0 & ? & ? & ? \\ 1 & 1 & 1 & ? & ? & ? \\ \end{array} $$ et cetera...

That's the thing. I know the states I want on the Q side should just go 0 - 7 in binary, but I can't get my head around what is happening in the flip flop.

That is, do we take the clock input as 0 to start with, so out first D flip flop input is 0 0, and that output (Q and Q') is then 0 0, and after that the clock is 1, so the Q' bit is now 1 and the Q bit (the one that feds back into D) is now 0, and then?????

dos the input 0 1 -- what happens? I tried to follow the reasoning given in the lecture and I am at my wit's end.

I know this might seem beginner level stuff but I have really tried looking up stuff online and it's no help, because everyone seems to use different terminology. So pretend I am the dumbest, dumbest student you ever met.

And yes I am supposed to use D flip flops.