I am new to digital logic and I am confused hot to construct CMOS equivalent for XNOR gate using AND, OR, and NOT gates.

I found XNOR circuit implemented with gates.

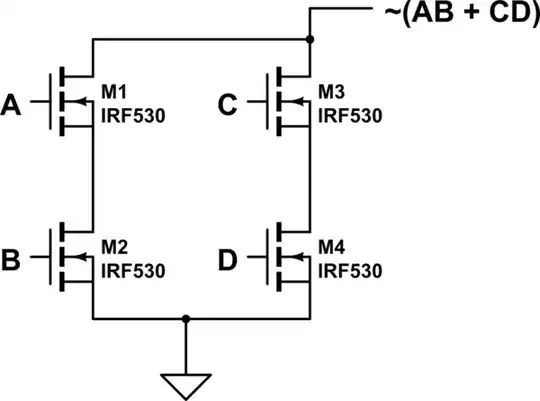

And what I did is I plugged CMOS circuits for inverter, AND and OR.

I doubt it is right thing to do.. but I have no idea how to do it other way. Need you help!