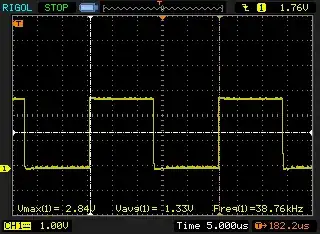

I don't think that the problem is related to the storage delay, because the working frequency is far too low (38 kHz according to capture) for this capacitance to show up.

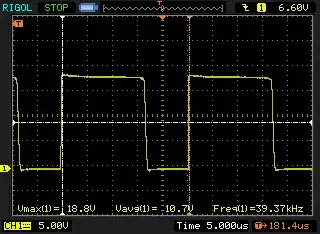

Looking to the diagram one notices that the base current in Q3 is very big. When it is turned ON, the base voltage is at 19.3 V. The current from base node to ground (through Q1) is about 19/R43=19 mA. Most of those 19 mA comes from Q3 base. And for this transistor (ic max = 100 mA, hfe=100 minimum), you only need 1 mA in base current to reach saturation current.

I would not be surprised if Q3 has been damaged. Also Q1 might be damaged if you had tried it with R37=0 Ohms! Also Q2 should have a resistor of 47 kOhms between base and pin PWM-ZV8 negated. It is also very likely damaged.

Those three transistors should be replaced and new values for resistor calculated. For instance:

R38=not populated, R37=47 kOhms, R43=18 kOhms, and a resistor of 47 kOhms for Q2.