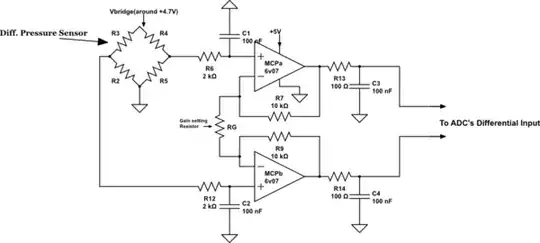

I am designing a pressure calibrator (my first Real project), which is supposed to measure from 0-200.00 mmWC (20000 counts) using Silabs C8051F350 (inbuilt 24-bit Sigma delta ADC). Sensor used is a typical Wheatstone bridge type Differential Pressure sensor.

This is the schematic to generate Bridge voltage (Vbridge) for the sensor. ADC-Vref seems to very be noisy on DSO (few mVp-p).

In almost all our instruments, previous Engineers have freely used AD620 to condition differential pressure signal, however cost of that INA has now increased too much for us to throw it randomly in our circuit so we have resorted to following arrangement. Common mode rejection to be dependent on ADC's PGA's CMRR, which is stated to be typical 100 dB at 50/60Hz BW.

simulate this circuit – Schematic created using CircuitLab

So here's my first question: Is this ADC driver, Vbridge generation a viable method. I mean is it going to give me good, less error, less noisy performance (because my step size with a 5mV full span sensor would be 0.25uV/step).

Sorry for using words like good and less, I can't speak actual number since noise voltage calculations and stuffs are above my head.

And my main concern is: We are deriving 5V from a single cell Li-ion and Boost converter(MCP1640) which also has few mVpp of ripple.

So is it an intelligent idea to use such a switching power supply in Analog sensitive instrument.