Three reasons come to mind:

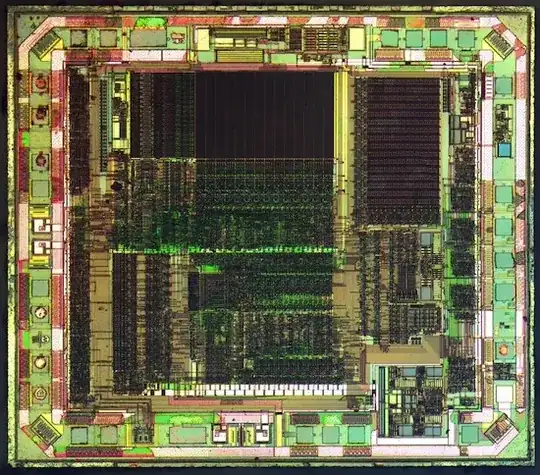

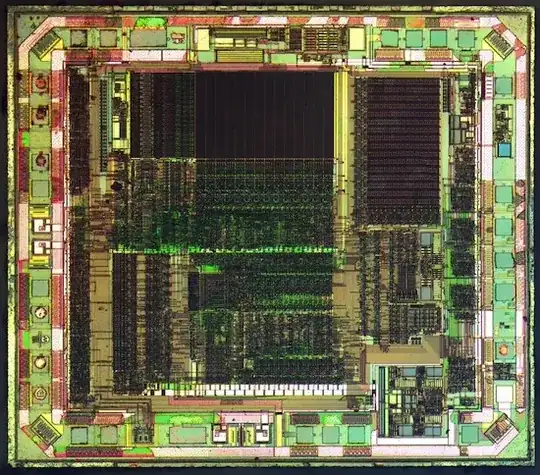

1) Take a look at this close-up of the guts of a microcontroller.

There's a LOT going on in there. And every part of that die needs power. Power coming in from any one pin will probably have to snake it's away around a lot of stuff to get to every part of the device. Multiple power lines gives the device multiple avenues to pull power from, which keeps the voltage from dipping as much during high current events.

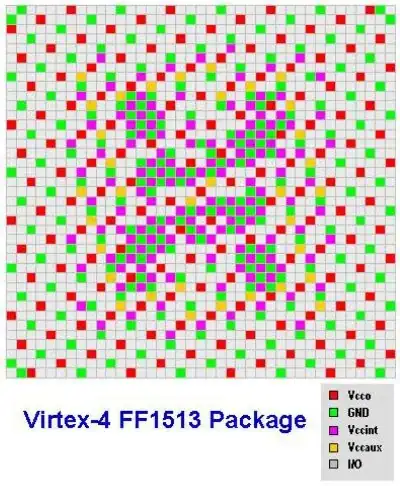

2) Sometimes the different power pins supply specific peripherals within the chip. This is done when certain peripherals need as clean a voltage supply as possible to operate correctly. If the peripherals share the power supply that the rest of the chip uses, it may be subject to noise on the line and voltage dips. An example is the analog power supply. You noticed it's typical to see an AVCC pin on MCUs. That pin is a dedicated supply just for the analog peripherals on the chip. Really, this is just an extension of #1 above.

3) It's not uncommon for an MCU to power its core at one voltage but operate peripherals at another. For example, an ARM chip I worked with recently used 1.8V for its core. However, the digital output pins would supply 3.3V when driven high. Therefore, the chip required a 1.8V supply and a separate 3.3V supply.

The main thing to remember is that all of those supply pins are absultely necessary to connect. They are not optional, even when doing development work.

As for the bottom pad on the chip, it's there for extra heat sinking. The chip designer decided that the casing and pins of the chip may not sink the heat away from the silicon enough. So the extra pad on the bottom acts like a heat sink to help keep the temperature down. If the part is expected to need to dissipate a lot of heat, you'd want to have a large copper pour to solder that pad onto.