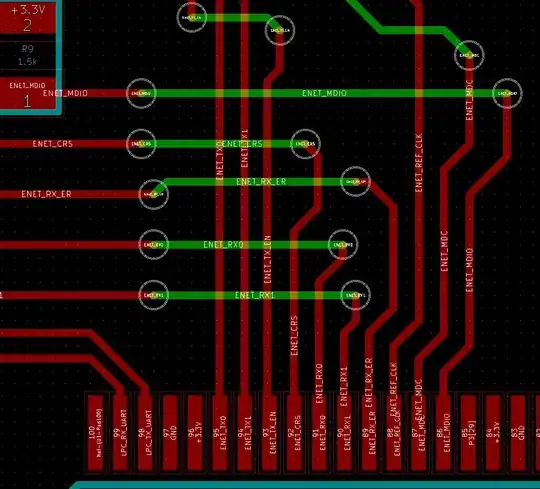

I have some signal integrity and EMC questions.

In my board LPC1768 RMII interface is connected to LAN8720. Because of pin locations some RMII signals must go through bottom layer. This is a four layer board, 2nd layer is GND, 3rd layer is Power. I know vertical traces reduce emi effects, so I routed this way. Since it is RMII, interface is 50Mhz.

In this routing maximum trace length is 2.15cm and minimum trace length is 1.75 cm, so max. difference between trace lenghts' is within 4mm. Trace width is 0.16mm. I used KiCAD's Pcb Calculator to calculate trace impedance and used data from Gold Phoenix PCB manufacturing. And impedance for these traces are 66 ohm(Differential impedance values for phy side RX/TX couples are 50ohm).

According to LAN8720 IBIS model, REF_CLK rise time is 2.104 ns and fall time is 1.296 ns

- Does REF_CLK must be routed without vias.

- Does REF_CLK need termination resistor?

- Is 4mm difference in trace length @50Mhz acceptable?

These are my questions, also please add any other opinions and comments.

(I saw old micropendousx reference designs, its a two layers board and using multiple vias almost all signals because its a very small board, I didn't use it, so I don't know if its working or not)

lpc1768 datasheet lan8720 datasheet micropendousX reference design