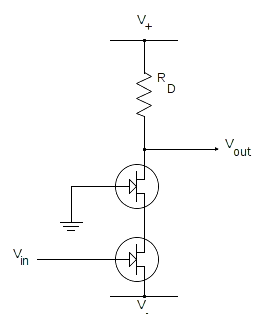

This has been bothering me for some time. Why is it that the overdrive voltage of the bottom transistor in a cascode controls the DC current, and not the Vgs of the top transistor? Similarly, in an NMOS diff pair with a current mirror on the bottom, why does the overdrive voltage of the mirror control the current, and not the common-mode voltage of the pair?

This came to mind when I read in a textbook that it is improper to draw a current source feeding the drain of a transistor, rather than pulling current from the source.