When to consider a digital signal fast enough to treat the interconnect (PCB trace) as a transmission line depends on two things:

- Electrical length of the signal

- Rise/fall-time (which is another way to say frequency content)

As a rule-of-thumb(*) whenever the electrical length of the trace is longer than some fraction of the rise/fall time, you will see reflections unless properly terminated. You can use 1/3 to 1/5 for the "fraction".

As an example: 4"/100mm trace is about 700ps of electrical length (use your favorite 2D field solver to find the exact number). If you launch a signal out of a semi-modern FPGA with say 300ps rise-time down that trace, you are sure to get reflections unless termination is used. In this case 1/5 of the rise-time is 60ps and the max trace length without significant reflections is about 8-9mm.

Make sure that you understand that the frequency of the signal is irrelevant. Reflections can happen with a 1Hz signal or a 500MHz signal - it's the same mechanism.

Now you can easily avoid reflections on a longer trace by using series or parallel termination. That is what we mean when we say treat the trace as a transmission line.

And you can easily do this with any impedance. There is nothing magical about 50R. That said, almost all modern digital signals can be routed in 50R and it's a lot easier to deal with only one impedance on any layer in a multilayer PCB.

As to your question about best practice: On boards connecting two or more modern digital parts, all traces are analyzed for signal integrity and routing rules are created before layout. In 99% of the cases I have analyzed, 50R is selected as trace impedance - even for differential pairs like USB, PCIe etc.

(*) Be careful with rules-of-thumb. Technology changes fast enough that you have to understand this stuff or you risk using an outdated rule-of-thumb.

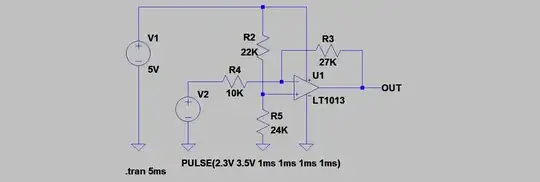

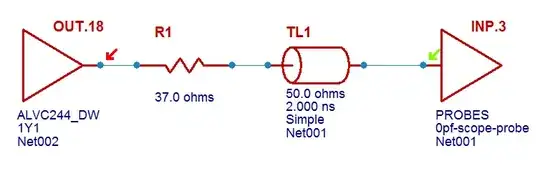

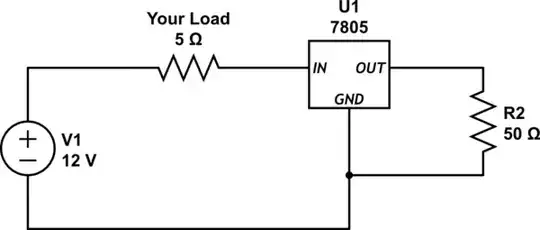

Just for the fun of it I ran some simple simulations for you in Mentor Hyperlynx. Here is the simple circuit:

Here is what happens if you do nothing (note the length of the trace/transmission line here is 2ns or roughly 1ft/30cm):

If we make the trace 60ps long (8-9mm) the reflections are almost gone:

Changing the impedance to some other value does not significantly change this picture. But if we want to use series or parallel termination, we need to know the trace impedance.

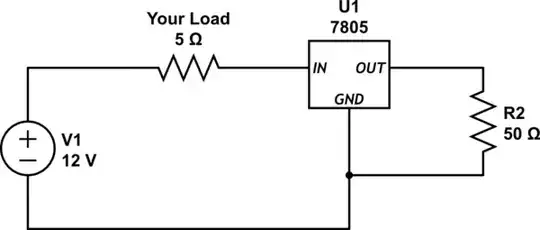

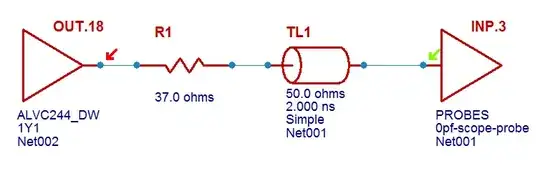

Lastly let me just show how it works with a series termination resistor. In this example, the series termination resistor is selected so the output impedance of the driver IC plus the series termination resistor matches the 50R of the trace:

The simulation comes out like this looking very nice even with this long trace: