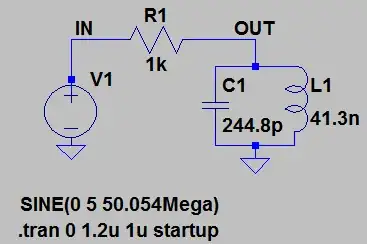

Using an LC parallel tank circuit from any voltage source will get loaded in parallel from the source series resistance. The maximum output signal will only be 0dB attenuation and only at precise resonant frequency with zero phase shift. Since phase shift goes from -90 to +90 over the 3dB bandwidth of the tank circuit, error frequency will produce a non-zero phase shift and attenuate from ideal 0 dB loss. You cannot get any gain from a voltage source.

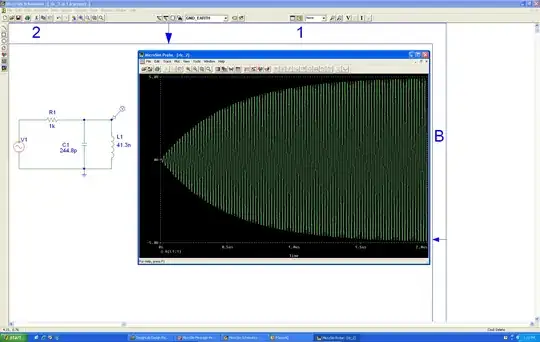

Since your simulation has a phase shift, it will also have attenuation according to the % error x Q.

For example of your circuit with cursor offset see attenuation and phase shift.

The proper use to achieve voltage gain* of an LC parallel resonant high Q circuit is to use a current source ( very high impedance) and similar very high impedance load, such as on a common emitter stage with L between collector to Vcc. Then the Q will be determined solely by the load Resistance /Reactance of either element at resonance and voltage gain determined by high ratio of collector load to emitter resistance.

The proper use to achieve voltage gain* of an LC parallel resonant high Q circuit is to use a current source ( very high impedance) and similar very high impedance load, such as on a common emitter stage with L between collector to Vcc. Then the Q will be determined solely by the load Resistance /Reactance of either element at resonance and voltage gain determined by high ratio of collector load to emitter resistance.

Start by choosing the load resistance and resonant frequency, then choose L or C according to desired Q then match the other reactive part for resonance.

For practical concerns Q=100 is easily achievable, which means only 2 or 3 significant figures for frequency, and not 5 as in your example. Stray capacitance MUST also be factored and L leakage capacitance or self resonant frequency, as well.

As an aside note, For crystals, and MEMS resonators ~ 10k for Q is normal. But when used in oscillators with say 1k series resistance the amplifier must have at least a gain of 10 to square up the sine input signal. This gain=10 is true in all CMOS gates unless they are buffered, i.e. 3stages or gain=1000. If you put your circuit in a CMOS inverter feedback loop, treat it as a voltage source. If using a BJT, treat it as a current source.

The proper use to achieve voltage gain* of an LC parallel resonant high Q circuit is to use a current source ( very high impedance) and similar very high impedance load, such as on a common emitter stage with L between collector to Vcc. Then the Q will be determined solely by the load Resistance /Reactance of either element at resonance and voltage gain determined by high ratio of collector load to emitter resistance.

The proper use to achieve voltage gain* of an LC parallel resonant high Q circuit is to use a current source ( very high impedance) and similar very high impedance load, such as on a common emitter stage with L between collector to Vcc. Then the Q will be determined solely by the load Resistance /Reactance of either element at resonance and voltage gain determined by high ratio of collector load to emitter resistance.