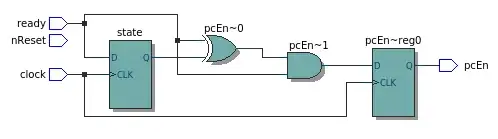

I have a fast clock and a switch called 'ready'. When the switch is flipped (ready goes HIGH), I would like the output pcEn to produce a pulse that lasts only for one clock cycle. pcEn will only output another pulse the next time ready goes HIGH again.

The following code simulates correctly, but is unfortunately not synthesizable. Note that space is an important consideration, so I was wondering if it's possible to implement it without using a state machine (which uses a lot of logic elements).

module control

(

output logic pcEn,

input clock, ready

);

always_ff @(negedge clock)

pcEn <= 1'b0;

always_ff @(posedge ready)

pcEn <= 1'b1;

endmodule