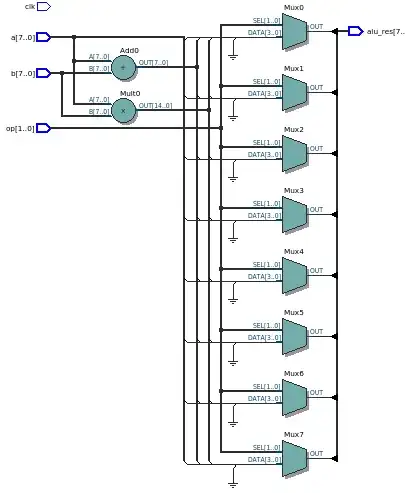

I'm trying to synthesize an Altera circuit using as few logic elements as possible. Also, embedded multipliers do not count against logic elements, so I should be using them. So far the circuit looks correct in terms of functionality. However, the following module uses a large amount of logic elements. It uses 24 logic elements and I'm not sure why since it should be using 8 + a couple of combinational gates for the case block.

I suspect the adder but I'm not 100% sure. If my suspicion is correct however, is it possible to use multipliers as a simple adder?

module alu #(parameter N = 8)

(

output logic [N-1:0] alu_res,

input [N-1:0] a,

input [N-1:0] b,

input [1:0] op,

input clk

);

wire [7:0] dataa, datab;

wire [15:0] result;

// instantiate embedded 8-bit signed multiplier

mult mult8bit (.*);

// assign multiplier operands

assign dataa = a;

assign datab = b;

always_comb

unique case (op)

// LW

2'b00: alu_res = 8'b0;

// ADD

2'b01: alu_res = a + b;

// MUL

2'b10: alu_res = result[2*N-2:N-1]; // a is a fraction

// MOV

2'b11: alu_res = a;

endcase

endmodule